ARM은 32비트 RISC(Reduced Instruction Set Computing) 마이크로프로세서 아키텍처이다. 초기에는 주로 저전력 소비를 위해 설계되었지만, 현재는 다양한 분야의 기기에서 널리 사용되고 있다. ARM 아키텍처에 대해 요약해 본다.

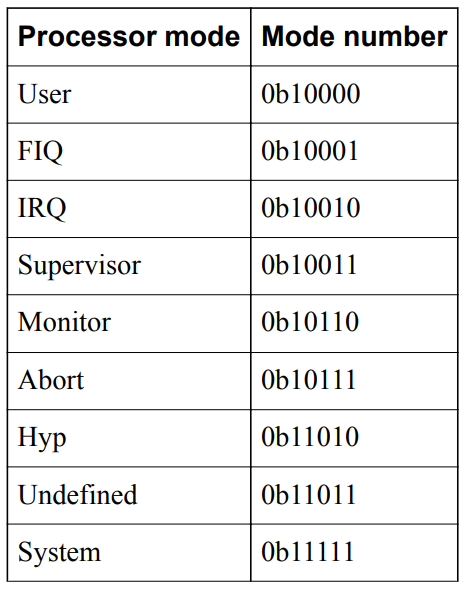

프로세서 모드

ARM 프로세서는 아키텍처 버전에 따라 9개 모드를 지원한다.

- User 모드: 일반적인 어플리케이션 실행 모드 (Non-privileged)

- Fast Interrupt 모드: 빠른 인터럽트 처리를 위한 모드

- Interrupt 모드: 범용 인터럽트 처리 모드

- Supervisor 모드: OS 보호 모드 (SW 인터럽트)

- Monitor 모드: 모니터 모드, real world와 secure world간 전환을 위한 모드

- Abort 모드: 데이터, 명령어 prefetch 중단 시

- Hypervisor 모드: 하이퍼바이저 모드

- Undefined 모드: 정의되지 않은 명령어 예외 발생 시

- System 모드: OS(Kernel)가 사용하는 모드

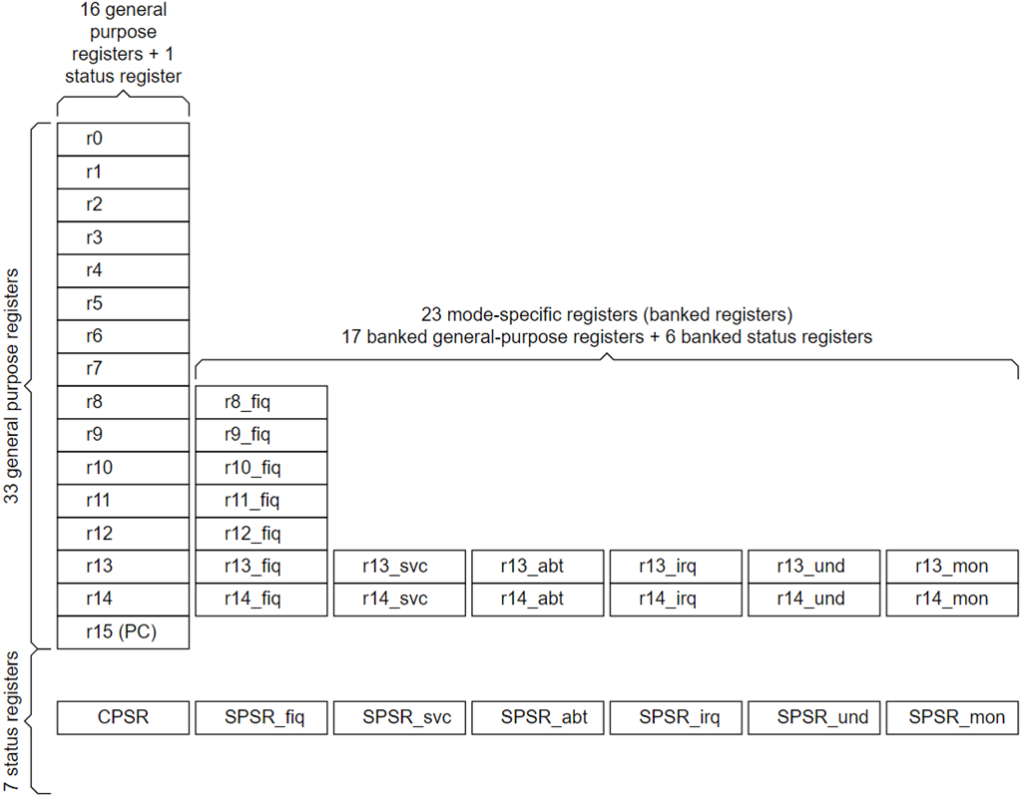

레지스터

- 15개의 범용 레지스터: R0~R12, R13(SP, Stack Pointer), R14(LR, Link Register), R15(PC, Program Counter)

- 프로그램 상태 레지스터: CPSR

모드별 레지스터에 대한 설명

ARM 아키텍처 모드에 따라 사용되는 레지스터는 다음과 같다.

레지스터 접근은 R0~R14 직접 접근하며, PC 사용이 허용된다. CPSR/SPSR의 접근은 특별한 명령어를 통해야 한다.

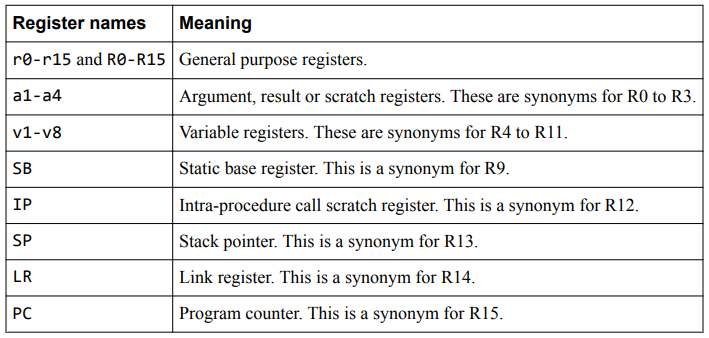

AAPCS에 의한 레지스터 사용

AAPCS(Procedure Call Standard for ARM Architecture) 에서는 다음 테이블과 같이 이름과 사용을 정의한다.

프로그램 카운트(PC)

- 모든 명령어는 길이가 32비트이고 메모리에 저장될 때 word(4 bytes)로 정렬되어야 한다.

- R15(PC) 값은 bit2~31에 저장되고, bit 0~1은 항상 0이다.

- R14(LR)은 BL instruction을 사용하여 서브루틴 호출 시 return 주소가 자동으로 저장된다.

BL SUB1 ; when call subroutine

MOV R15, R14 ; when return from subroutineQ 플래그

- APSR 상태 플래그 중 하나로, Overflow나 Saturation을 표기한다.

- sticky flag

Q 플래그를 clear 하기 위해서는 아래와 같이 MSR 명령어를 사용해야 한다.

MRS r5, APSR

BIC r5, r5, #(1<<27)

MSR APSR_nzcvq, r5Q 플래그 상태는 condition codes에서 직접 읽어 올 수는 없고, MRS 명령으로 register에 읽어와 사용해야 한다.

MRS r6, APSR

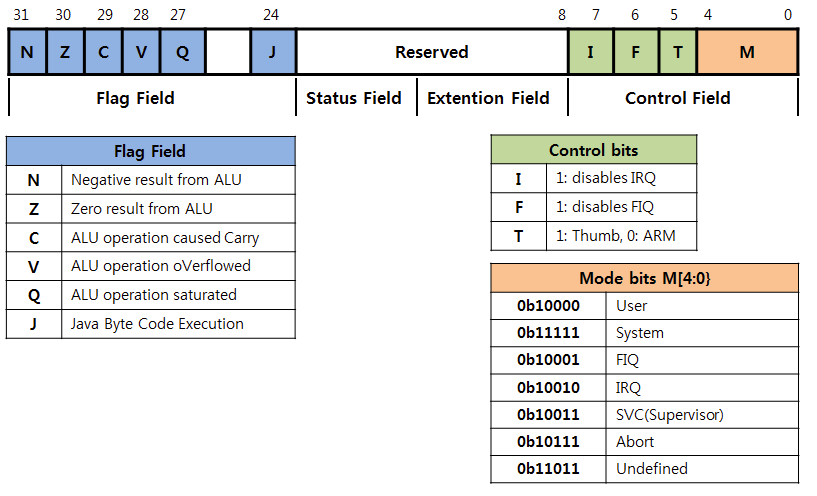

TST r6, #(1<<27); Z is clear if Q flag was set프로그램 상태 레지스터(PSR, Program Status Registers)

PSR 레지스터는 크게 Flag 필드와 Control 필드로 나눌 수 있다.

- Flag 필드: ARM 명령어 수행 후 상태를 나타내 준다. 이러한 상태들은 다음 명령어의 조건이 되어 동작하게 된다.

- Control 필드: Control 비트 와 모드 비트로 나뉜다.

- Control 비트: IRQ/FIQ disable 을 제어하거나, Thumb/ARM 인지를 표기한다.

- Mode 비트: 현재 모드를 표기한다.

익셉션 핸들링(Exception Handling) 과 벡터 테이블(Vector Table)

ARM에서 익셉션이 발생하면:

- 모드 변경: CPSR를 SPSR_<mode>로 copy한다.

- CPSR 설정

- ARM state 진입

- Mode bit 설정

- Interrupt disable

- Return Address를 LR_<mode>에 저장한다.

- PC를 Vector Address로 저장한다.

익셉션 처리가 끝난 후 복귀하려면:

- SPSR_<mode>로 부터 CPSR을 복원한다.

- LR_<mode>를 PC로 복원한다.

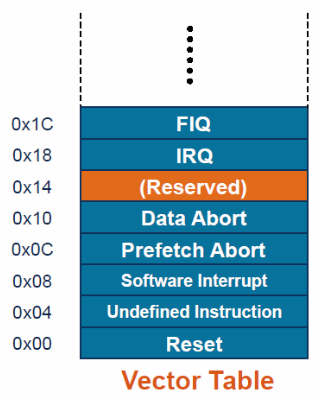

다음은 익셉션 벡터 테이블이다.

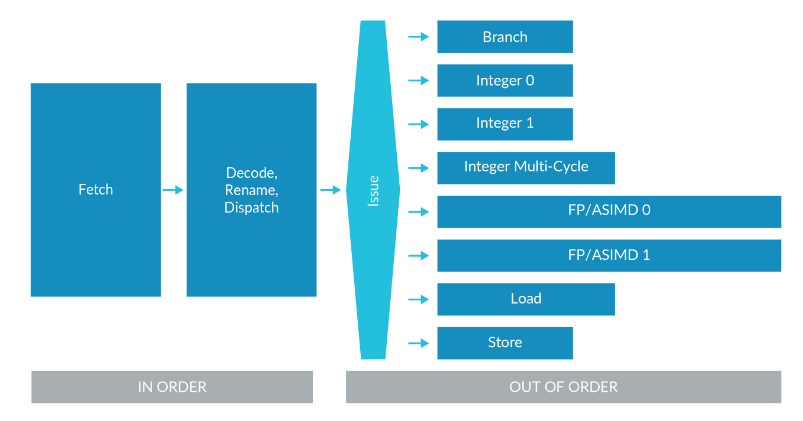

명령어 파이프라인(Instruction Pipeline)

ARM 아키텍처는 하나의 명령어를 여러개의 독립적인 작업들을 pipeline 으로 나뉘어 병렬적으로 한 cycle에 하나씩 순차적으로 실행함으로서 프로세서 속도를 획기적으로 개선한다. ARM 아키텍처 버전에 따라 pipeline수는 다르다.

주의: PC는 실행 위치가 아닌 Fetch 위치를 가르킨다.